# SIMATIC NET

# DPC31 Siemens PROFIBUS-DP Controller with C31 Core

Hardware Description

Date 12/14/00

# SIMATIC NET

# DPC31- Hardware Description

(Siemens PROFIBUS-DP Controller with integrated C31 Core according to EN 50170 Volume 2)

> Version: 1.0 Date: 12/00

#### **Liability Exclusion**

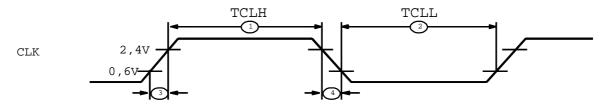

We have tested the contents of this document regarding agreement with the hardware and software described. Nevertheless, deviations can't be ruled out, so that we are not guaranteeing complete agreement. However, the data in this document is checked periodically. Required corrections are included in subsequent editions. We gratefully accept suggestions for improvement.

#### Copyright

Copyright (C) Siemens AG 2000. All rights reserved

Unless permission has been expressly granted, passing on this document or copying it, or using and sharing its content is not allowed. Offenders will be held liable. All rights reserved, in the event a patent is granted, or a utility model or design is registered.

The trade marks SIMATIC, SINEC L2 are protected by law for Siemens through application/registration.

All other product and system names are (registered) trade marks of their respective proprietors, and are to be treated as such.

Subject to technical change.

# **Versions**

| Version Nr. | Date     | Page | Information                                             |

|-------------|----------|------|---------------------------------------------------------|

| 0.x         |          |      | first Version                                           |

| 1.0         | 14.12.00 |      | RS485 wiring corrected RXD_RXS und XCTS_RXA Data Buffer |

# Inhaltsverzeichnis

| 1 | INT                                                              | RODUCTION                                                                                                                                                                                                                                                                                                              | 7                                                              |

|---|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 2 | ΟV                                                               | ERVIEW                                                                                                                                                                                                                                                                                                                 | 8                                                              |

|   | 2.1                                                              | General Data                                                                                                                                                                                                                                                                                                           | 8                                                              |

|   | 2.2                                                              | Differences Between the DPC31 and the SPC3/SPC4                                                                                                                                                                                                                                                                        | 8                                                              |

|   | 2.3                                                              | Function Overview (Block Diagram)                                                                                                                                                                                                                                                                                      | 9                                                              |

|   | 2.4                                                              | Pin Description                                                                                                                                                                                                                                                                                                        | 11                                                             |

| 3 | ME                                                               | MORY ASSIGNMENT                                                                                                                                                                                                                                                                                                        | 12                                                             |

|   | 3.1                                                              | Memory Area Distribution in the DPC31                                                                                                                                                                                                                                                                                  | 12                                                             |

|   | 3.2                                                              | Control Unit Parameters (Latches/Registers)                                                                                                                                                                                                                                                                            | 12                                                             |

|   | 3.3                                                              | Organizational Parameters (RAM)                                                                                                                                                                                                                                                                                        | 14                                                             |

| 4 | AS                                                               | IC INTERFACE                                                                                                                                                                                                                                                                                                           | 20                                                             |

| 5 | СО                                                               | MMUNICATION FUNCTIONS OF THE SEQUENTIAL CONTROL SYSTEM                                                                                                                                                                                                                                                                 | 21                                                             |

|   | 5.1<br>5.1.<br>5.1.<br>5.2<br>5.2<br>5.2.<br>5.2.<br>5.2.<br>5.2 | Request Interface for DPS (Instruction Queue) Acknowledgement Interface (Indication_Queue)  DPS Module, Description of the Interface Set_Slave_Address, SSA (SAP55) Set_Param, Prm (SAP61) Check_Config, CCFg (SAP62) Slave_Diagnosis (SAP60) Write_Read_Data (Default SAP) Global_Control (SAP58) Read_Inputs (SAP56) | 21<br>21<br>21<br>23<br>24<br>25<br>26<br>28<br>29<br>31<br>33 |

| _ | 5.2.5<br>5.2.5                                                   | 9 Get_Config (SAP59)                                                                                                                                                                                                                                                                                                   | 33<br>33                                                       |

| 6 | US                                                               | ER FUNCTIONS ON THE C31 CONTROLLER                                                                                                                                                                                                                                                                                     | 34                                                             |

| DESCRIPTION OF THE HARDWARE BLOCKS                                                                                                                                                                                                                                         | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.1 Universal Processor Interface                                                                                                                                                                                                                                          | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.1.1 Bus Interface Unit (BIU)                                                                                                                                                                                                                                             | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.1.2 IO Interface                                                                                                                                                                                                                                                         | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                            | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.1.4 Interrupt Controller of the μP Interface in the DPC31                                                                                                                                                                                                                | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.2 Synchronous Serial Interface (SSC Interface)                                                                                                                                                                                                                           | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.3 80C31 Core and Interface                                                                                                                                                                                                                                               | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                            | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| •                                                                                                                                                                                                                                                                          | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| · ·                                                                                                                                                                                                                                                                        | 51<br>51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.5.4 Interface Signals                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.4 C31 Interrupt Controller in the DPC31                                                                                                                                                                                                                                  | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.5 Serial PROFIBUS Interface                                                                                                                                                                                                                                              | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                            | 52<br>53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.6 DPS Watchdog Timer                                                                                                                                                                                                                                                     | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.7 Watchdog Timer                                                                                                                                                                                                                                                         | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                            | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| •                                                                                                                                                                                                                                                                          | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.7.3 Response Monitoring                                                                                                                                                                                                                                                  | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.8 Clock Supply                                                                                                                                                                                                                                                           | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7.8.1 PLL                                                                                                                                                                                                                                                                  | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TEST SUPPORT                                                                                                                                                                                                                                                               | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.1 Emulator Connection for the C31                                                                                                                                                                                                                                        | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ELECTRICAL SPECIFICATIONS                                                                                                                                                                                                                                                  | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ELECTRICAL SPECIFICATIONS                                                                                                                                                                                                                                                  | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9.1 Maximum Limits                                                                                                                                                                                                                                                         | <b>65</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9.1 Maximum Limits 9.2 Permitted Operating Values                                                                                                                                                                                                                          | 65<br>66<br>66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.1 Maximum Limits 9.2 Permitted Operating Values 9.3 Guaranteed Operating Range for the Specified Parameters                                                                                                                                                              | 65<br>66<br>66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.1 Maximum Limits 9.2 Permitted Operating Values 9.3 Guaranteed Operating Range for the Specified Parameters 9.4 Power Loss 9.5 Pad Cells 9.5.1 Power-Up of the Supply Voltage                                                                                            | 65<br>66<br>66<br>66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9.1 Maximum Limits 9.2 Permitted Operating Values 9.3 Guaranteed Operating Range for the Specified Parameters 9.4 Power Loss 9.5 Pad Cells 9.5.1 Power-Up of the Supply Voltage 9.5.2 Structure of the Pad Cells with 5V Tolerance                                         | 65<br>66<br>66<br>66<br>67<br>67<br>67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9.1 Maximum Limits 9.2 Permitted Operating Values 9.3 Guaranteed Operating Range for the Specified Parameters 9.4 Power Loss 9.5 Pad Cells 9.5.1 Power-Up of the Supply Voltage                                                                                            | 65<br>66<br>66<br>66<br>67<br>67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9.1 Maximum Limits 9.2 Permitted Operating Values 9.3 Guaranteed Operating Range for the Specified Parameters 9.4 Power Loss 9.5 Pad Cells 9.5.1 Power-Up of the Supply Voltage 9.5.2 Structure of the Pad Cells with 5V Tolerance 9.5.3 DC Specification of the Pad Cells | 65<br>66<br>66<br>66<br>67<br>67<br>67<br>69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9.1 Maximum Limits 9.2 Permitted Operating Values 9.3 Guaranteed Operating Range for the Specified Parameters 9.4 Power Loss 9.5 Pad Cells 9.5.1 Power-Up of the Supply Voltage 9.5.2 Structure of the Pad Cells with 5V Tolerance 9.5.3 DC Specification of the Pad Cells | 65<br>66<br>66<br>66<br>67<br>67<br>67<br>69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7 7 7 7 7                                                                                                                                                                                                                                                                  | <ul> <li>7.1.1 Bus Interface Unit (BIU)</li> <li>7.1.2 IO Interface</li> <li>7.1.3 Interface Signals</li> <li>7.1.4 Interrupt Controller of the μP Interface in the DPC31</li> <li>7.2 Synchronous Serial Interface (SSC Interface)</li> <li>7.3 80C31 Core and Interface</li> <li>7.3.1 Reset Phase of the C31</li> <li>7.3.2 80C31 Core and Internal Memory</li> <li>7.3.3 Expansion Interface to the 80C31 Core</li> <li>7.3.4 Interface Signals</li> <li>7.4 C31 Interrupt Controller in the DPC31</li> <li>7.5 Serial PROFIBUS Interface</li> <li>7.5.1 Asynchronous Physics Unit (NRZ)</li> <li>7.5.2 Synchronous Physics Unit (Manchester)</li> <li>7.6 DPS Watchdog Timer</li> <li>7.7.1 Automatic Baudrate Detection</li> <li>7.7.2 Baudrate Monitoring</li> <li>7.7.3 Response Monitoring</li> <li>7.8.1 PLL</li> </ul> |

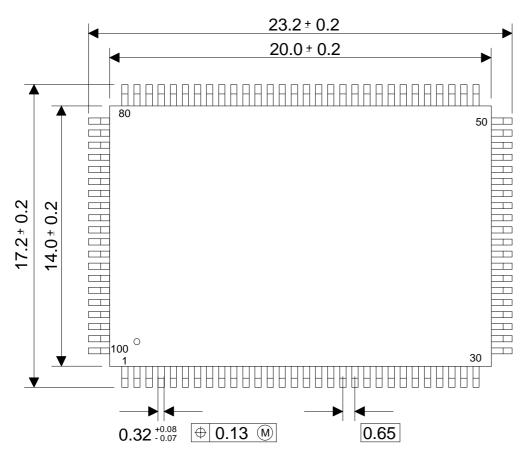

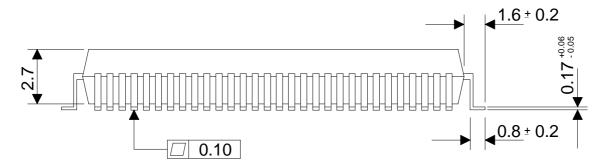

| 10 MECHANICAL SPECIFICATION                                 | 82       |

|-------------------------------------------------------------|----------|

| 10.1 PQFP 100 Casing                                        | 82       |

| 11 DPC31 PINOUT                                             | 83       |

| 12 APPLICATION NOTES                                        | 84       |

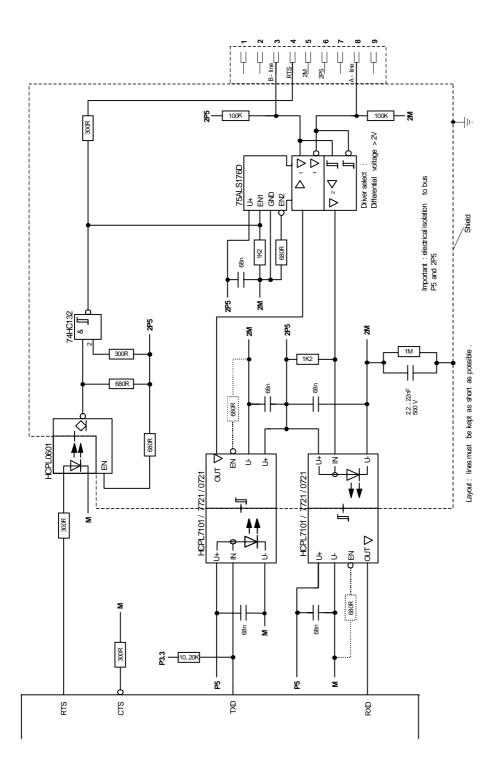

| 12.1 DPC31 Wiring                                           | 84       |

| 12.2 PROFIBUS Interface                                     | 84       |

| 12.2.1 Pin Assignment 12.2.2 Wiring Example RS485 Interface | 84<br>86 |

| 12.2.2 Willing Example 100400 interface                     | 00       |

| 13 APPENDIX                                                 | 88       |

| 13.1 Addresses                                              | 88       |

| 13.2 General Definitions of Terms                           | 89       |

| 13.3 Order Numbers                                          | 89       |

## 1 Introduction

Siemens offers to its users several ASICs for data exchange between automation devices that, on the basis of EN 50170 Volume 2, support or completely process the data traffic between the individual automation stations.

To support intelligent master/slave solutions, that is implementations with a micro-processor, the following ASICs are available. All ASICs do the following: support the transmission rates of 9.6 kBits/s ... 12000 kbit/s, autonomously set themselves to the transmission rate specified by the master and monitor it. After these ASICs receive a correct message, they autonomously generate the requested response messages.

In the **ASPC2** (Advanced Siemens PROFIBUS Controller), many components of Layer2 of the OSI model are already integrated according to ISO, but it still needs the support of a processor. This ASIC supports baudrates up to 12000 kbit/s; however, in its complexity, it is conceived more for master applications.

The **SPC3** (Siemens PROFIBUS Controller), through the integration of the complete PROFIBUS DP slave protocol, considerably relieves the processor of an intelligent PROFIBUS slave.

However, in the field of automation, there are also simple devices such as switches, thermoelements, etc. that do not require a microprocessor for recording their states.

For a low cost adaptation of such devices, two additional ASICs are available: the **SPM2** (Siemens PROFIBUS Multiplexer, Version 2) and **LSPM2** (Lean Siemens PROFIBUS Multiplexer). These chips process as DP slaves in the bus system.

The LSPM2 has the same functions as the SPM2 but with a lower number of I/O and diagnostic ports.

The **DPC31** (<u>DP</u> Controller with integrated 80<u>31</u> core) is a highly integrated PROFIBUS slave ASIC. The DPC31 is a slave controller for both PROFIBUS DP/DPV1 and PA applications.

The uses of this chip cover a wide area. On the one hand, it can be used for simple, intelligent applications that make do with the integrated C31 core.

On the other hand, it can be used for high performance slave solutions that have increased communication requirements. This requirement is met with an internal RAM that has been increased to 6kByte.

Approximately 5.5kByte of communication memory is available to the user.

#### The DPC31 has the following main features:

- integrated standard C31 core with an additional 3<sup>rd</sup> timer (Timer 2)

- low processor load through the integration of the complete DP slave protocol

- simple processor interface for a large number of processors:

INTEL: 8032, Siemens: C166

Motorola: HC11, HC16, HC916

- SSC interface (SPI) for interfacing serial EEPROMs, A/D converters, etc.

- integration of synchronous as well as asynchronous bus physics

This document explains the hardware configuration and the wiring of the DPC31.

In addition, Siemens offers a separate software package that relieves the user of local H/W register manipulations and memory calculations. The package provides a convenient C-interface for interfacing Profibus communication with the slave process.

80x86

# 2 Overview

#### 2.1 General Data

Package: 100 Pin PQFP

Baudrate: Asynchronous: 9.6, 19.2, 45.45, 93.75, 187.5, 500 kBd, 1.5, 3, 6 & 12 MBd

Synchronous: 31.25 kBd

Bus Interface: 8-Bit asynchronous/synchronous Intel and Motorola interface

C31 Ports: Standard Port Interface (4 Ports) for external memory expansion and emulator

interface

SSC Interface: Synchronous serial interface (SPI) for connecting serial E<sup>2</sup>PROMs, A/D converters,

etc.

Memory Area 6 kByte (approx. 5.5 kByte utilizable) can be directly addressed and can be broken

down into data and code memory

Environmental Cond.: 3.3V ±10%; -40 to +85 °C

#### 2.2 Differences Between the DPC31 and the SPC3/SPC4

| Characteristics                | DPC31                                | SPC3                     | SPC4                     |

|--------------------------------|--------------------------------------|--------------------------|--------------------------|

| General:                       |                                      |                          |                          |

| Package                        | 100 Pin PQFP                         | 44 Pin PQFP              | 44 Pin PQFP              |

| External µP Interface          | parallel, 8 bits                     | parallel, 8 bits         | parallel, 8 bits         |

| Family                         | Siemens, Intel, Motorola             | Siemens, Intel, Motorola | Siemens, Intel, Motorola |

| Preprocessing                  | yes, via int. C31                    | no                       | no                       |

| External Memory                | yes, Flash, RAM etc.                 | no                       | no                       |

| Expansion (C31)                | 2                                    |                          |                          |

| SSC Interface (SPI)            | yes, for example E <sup>2</sup> PROM | no                       | no                       |

|                                | up to 64 kByte,                      |                          |                          |

|                                | A/D conv. (AD7714)                   |                          |                          |

| I/O Interface                  | yes, up to 40 bits                   | no                       | no                       |

| Internal PLL                   | yes, input 12 MHz                    | no                       | no                       |

| Communication RAM              | max. 5.5 kByte                       | 1.4 kByte                | 1.14 kByte               |

| l                              |                                      |                          | (1.64 for SPC41)         |

| PB Communication:              |                                      |                          |                          |

| Baudrate                       | 0.01.014.40.140.1                    | 0.01.014.40.140.1        | 0.01.014.40.140.1        |

| async. RS485                   | 9.6 kBd to 12 MBd                    | 9.6 kBd to 12 MBd        | 9.6 kBd to 12 MBd        |

| sync. Manchester               | 31.25kBd                             | no                       | 31.25 kBd                |

| DP Slave                       | fully integrated                     | fully integrated         | partially integrated     |

| Receive Resources              | exchange buffer                      | exchange buffer          | polling list             |

| Receive Resources              | exchange buller                      | exchange buller          | politing list            |

| Integrated User                |                                      |                          |                          |

| Functions:                     |                                      |                          |                          |

| E <sup>2</sup> PROM Read/Write | ves                                  | no                       | no                       |

| DPV1 Protocol                  | Available in FW                      | no                       | no                       |

|                                |                                      |                          |                          |

Table 2.2-1: Differences with respect to SPC3 and SPC4

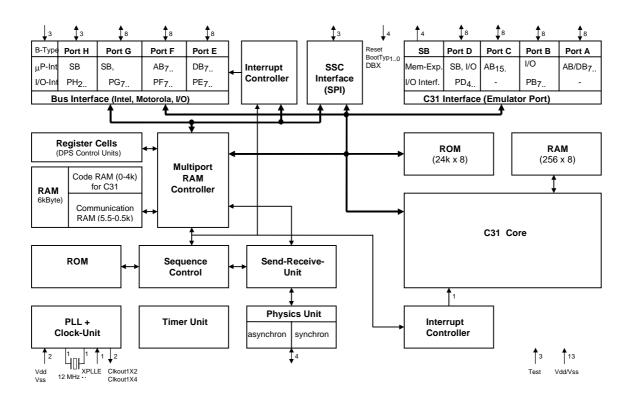

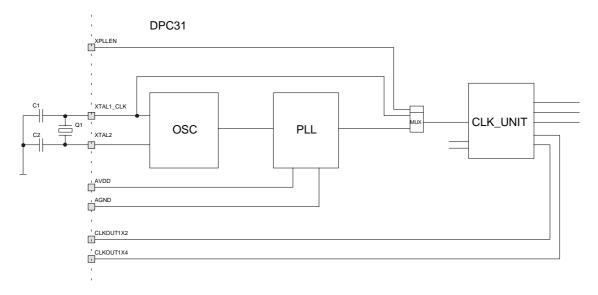

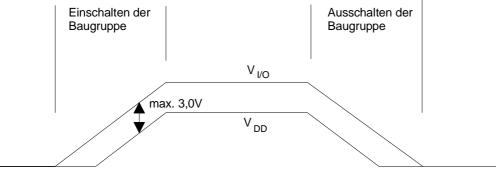

#### 2.3 Function Overview (Block Diagram)

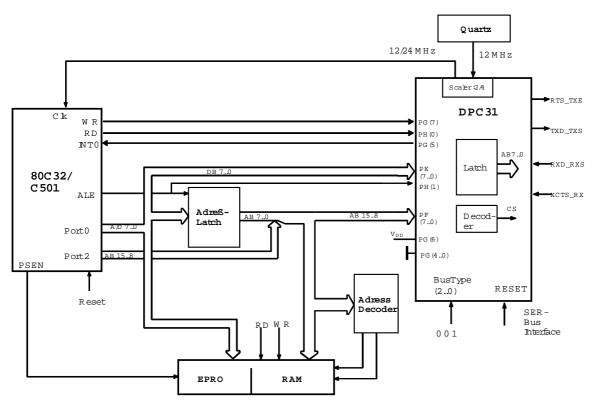

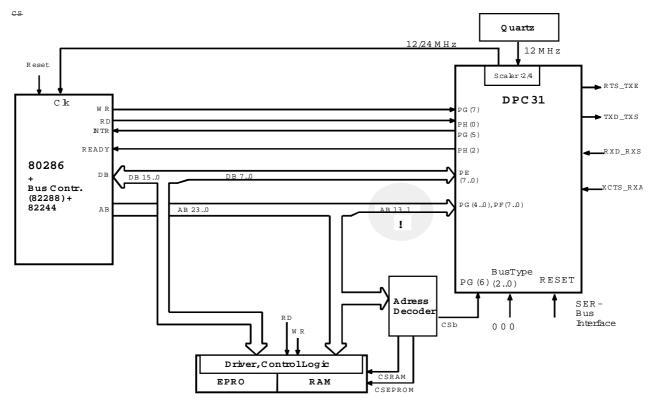

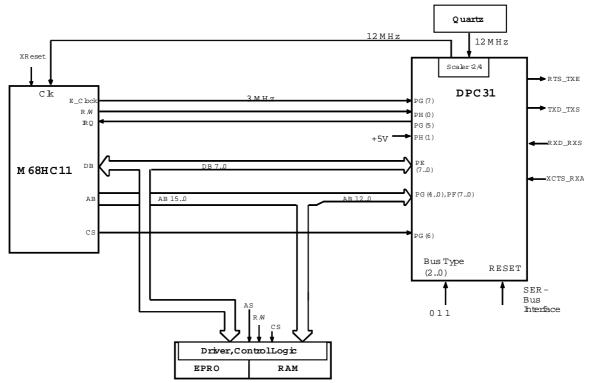

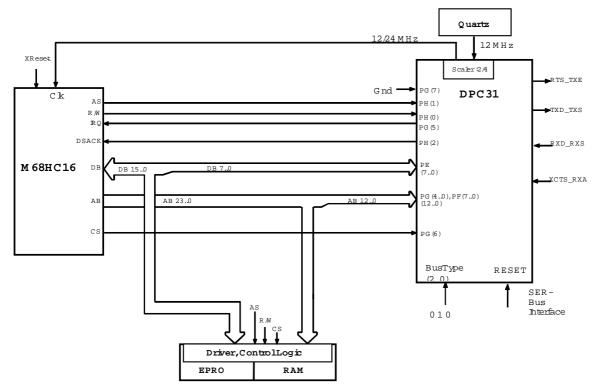

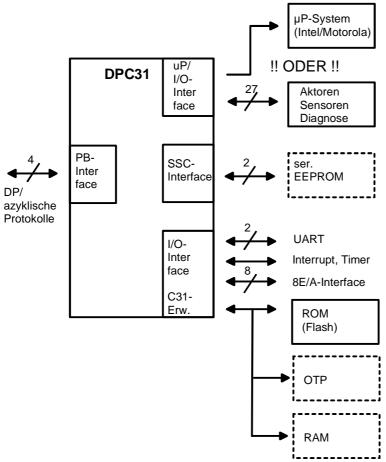

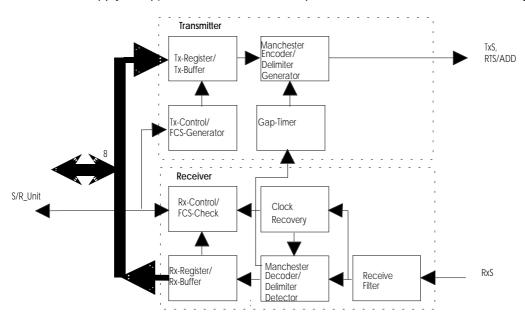

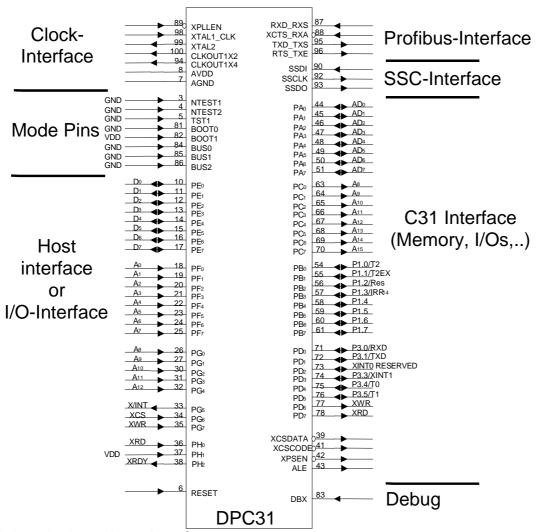

Figure 2.3-1 shows the block diagram of the DPC31. The DPC31 has a **bus interface** for connecting an external micro-processor. It is a parameterizable, synchronous/asynchronous 8-bit interface for various Siemens, Intel, and Motorola micro-controllers/processors. Via the 13-bit address bus, the user can directly access the internal 5.5k RAM or the register cells. If the application does not need an external processor, the ports of the bus interface can be used as I/O. This makes 27 I/O bits available that the internal C31 can address individually.

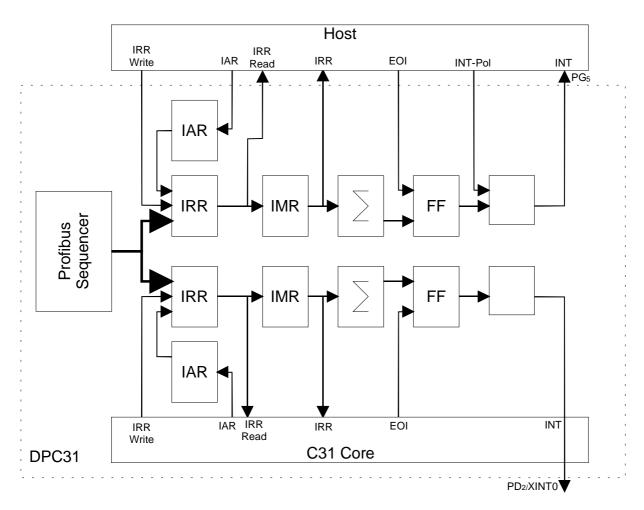

The sequence control enters various events (for example, indication events, error events, etc.) in the **interrupt controller** that are signalled to the slave firmware via the interrupt pin. These events can be enabled individually via a mask register. Acknowledgement is made via the acknowledge register.

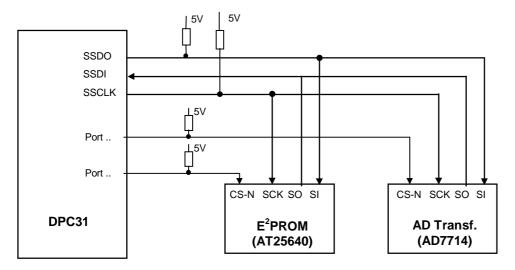

The **SSC interface (SPI)** is used for connecting a serial E<sup>2</sup>PROM or an A/D converter (such as AD7714). This interface is laid out only as a master interface.

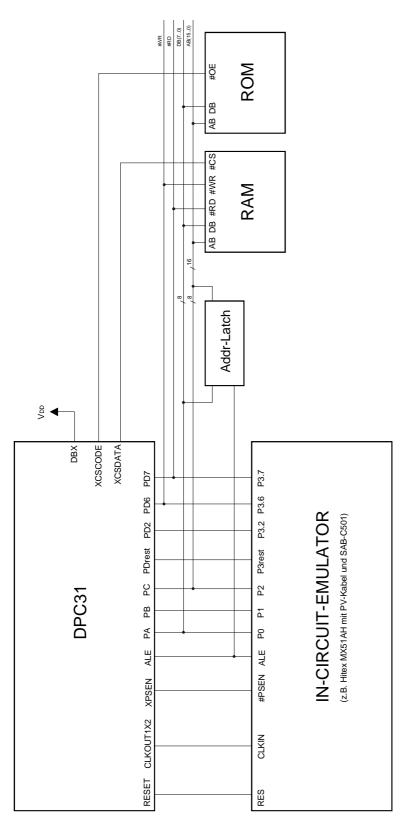

The **C31** interface includes the ports of the standard controller. Via this interface, an external memory- and I/O expansion can be implemented. Via corresponding CS signals, the code and data address areas are coded out that are not used internally. In addition, up to 13 bits of I/O can be connected via these ports. The C31/32 emulator (Hitex etc.) is also controlled via this interface.

Via the **register cells**, the following are accessed: internal registers, the DPS(DP Slave) control units and the SSC module. The DPS control units represent the user interface to the DPS layer that is implemented via individual buffers. These control units exchange the buffers.

The integrated **C31** is fully compatible with the standard microcontroller. Also integrated is a **256 byte data RAM**. Via a second **interrupt controller**, the interrupt events mentioned above can also be entered in the C31. This makes it possible to distribute interrupt events between an external and an internal application.

The **bus physics unit** includes the asynchronous Layer1 (RS485: 9.6kBd to 12 MBd) and the synchronous Layer1 (IEC 1158-2; Manchester encoded: 31.25kBd) which also allows the chip to be operated in an intrinsically safe environment.

In the **clock unit**, an analog **PLL** is integrated, to which an external 12MHz quartz must be connected. With it, the PLL generates the internal 48MHz clock pulse for the asynchronous mode. In the synchronous mode, the PLL is switched off and an external clock pulse of 4 to 16 MHz is applied. In addition, power management is implemented in the clock unit which switches off internal clock pulses in certain states. As outputs, the internal working clock pulse divided by 2 and by 4 is available.

Figure 2.3-1: Block Diagram DPC31

#### 2.4 Pin Description

The DPC31 has a 100 pin PQFP package with the following signals:

| Function Group   | Name         | Pins | Type | Voltage<br>Proof | Function                                         |

|------------------|--------------|------|------|------------------|--------------------------------------------------|

| C31 Interface    | PA           | 8    | I/O  | 5V               | Corresponds to P0 for the discrete type          |

|                  | PB           | 8    | I/O  | 5V               | Corresponds to P1 for the discrete type          |

|                  | PC           | 8    | I/O  | 5V               | Corresponds to P2 for the discrete type          |

|                  | PD           | 8    | I/O  | 5V               | Corresponds to P3 for the discrete type          |

|                  | ALE          | 1    | I/O  | 5V               | Address Latch Enable                             |

|                  | XPSEN        | 1    | I/O  | 5V               | For emulation only                               |

|                  | XCSDATA      | 1    | 0    | 5V               | Chip select for external RAM                     |

|                  | XCSCODE      | 1    | 0    | 5V               | Chip select for external ROM                     |

|                  | BOOTTYP      | 2    | l l  | 5V               | Type for loading the user program                |

|                  | DBX          | 1    | - 1  | 5V               | Switch to In Circuit Emulator                    |

| μP Interface     | PE           | 8    | I/O  | 5V               |                                                  |

|                  | PF           | 8    | I/O  | 5V               |                                                  |

|                  | PG           | 8    | I/O  | 5V               |                                                  |

|                  | PH           | 3    | I/O  | 5V               |                                                  |

| 0001.4.4         | BUSTYP       | 3    | 1    | 5V               | 0                                                |

| SSC Interface    | SSCLK        | 1    | 0    | 5V               | Connection for SPI Chips, Clock                  |

|                  | SSDO         | 1    | 0    | 5V               | Connection for SPI Chips, Data_Out               |

| 5 6              | SSDI         | 1    | !    | 5V               | Connection for SPI Chips, Data_In                |

| PLL + Clock Unit | XTAL1_CLK    | 1    | 1    | 3.3V             | Quartz connection / Clock supply                 |

|                  | XTAL2        | 1    | 0    | 3.3V             | Quartz connection                                |

|                  | AVDD         | 1    |      |                  | Separate V <sub>DD</sub> supply for PLL          |

|                  | AGND         | 1    |      |                  | Separate GND supply for PLL                      |

|                  | XPLLEN       | 1    | ı    | 5V               | Switching off the PLL and supply clock pulse via |

|                  | 011(01174)(0 |      |      | <b>5</b> ) (     | XTAL1_CLK                                        |

|                  | CLKOUT1X2    | 1    | 0    | 5V               | Clock pulse output CLK/2 (without reset)         |

| DI 1 11 11       | CLKOUT1X4    | 1    | 0    | 5V               | Clock pulse output CLK/4 (without reset)         |

| Physics Unit     | RTS_TXE      | 1    | 0    | 3.3V             |                                                  |

|                  | TXD_TXS      | 1    | 0    | 3.3V             |                                                  |

|                  | XCTS_RXA     | 1    | !    | 5V               |                                                  |

|                  | RXD_RXS      | 1    | ı    | 5V               |                                                  |

| General          | RESET        | 1    |      | 5V               | Reset Input                                      |

| Test             | NTEST1       | 1    | I    | 5V               | Test Pin                                         |

|                  | NTEST2       | 1    | I    | 5V               | Test Pin                                         |

|                  | TST1         | 1    | ı    | 5V               | Test Pin                                         |

| Supply           | VDD          | 4    |      |                  | +3.3V                                            |

|                  | GND          | 9    |      |                  | 0V                                               |

| Total            |              | 100  |      |                  |                                                  |

Figure 2.4-1: DPC31 Pin List

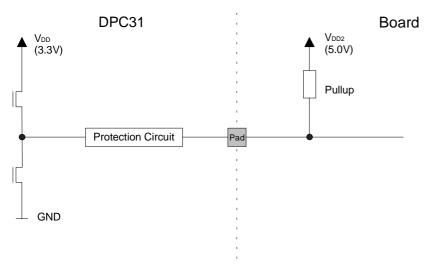

Because of the 5V-tolerant I/O, and in order to ensure the least possible power loss, no pull-up or pull-down resistors are integrated in the pad cells; that is, <u>all</u> unused inputs or all output ports (since these are switched as input after reset) are to be applied to one defined level (Ports A, B, D, E, F, G, and H). This is not necessary for Port C since it is permanently configured as output. A bus contention is permitted for a maximum of 20ns.

# 3 Memory Assignment

### 3.1 Memory Area Distribution in the DPC31

Table 3.1-1 shows the distribution of the internal 8k address space of the DPC31. Via this address space, the user interface to communication (DPS) is mapped. It does not matter whether the user program is running internally on the C31 or on the external micro-processor; the interface is identical in both cases.

The address area is subdivided into a 2K address space for the register cells and a 6k address space for the internal RAM. The internal registers (interrupt controller, Mode Register1, DPS control units, SSC interface) are located in the register area. Certain registers can only be read or written.

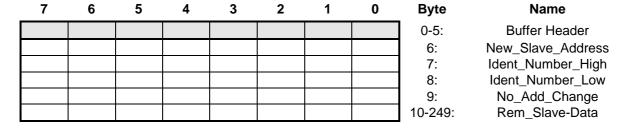

The RAM starts at address 800h. In the first area, the internal work cells are located (bit array, variables). The user is not to access this area. The sequential control system uses these cells for processing the protocol. Starting with address 0840h, the organizational parameters (parameter cells, buffer ptr(pointer) are located in the RAM. In the parameter cells, general parameter assignment data is transferred (Param Register, station address, Ident No., etc.), or status displays are stored (status register, GC\_Command, Score\_Register, etc.). The buffer pointers describe the entire buffer management for the SAPs. At address 08A0H, the buffers generated by the user start, corresponding to the parameter assignment of the organizational parameters. The sequence of the buffers can be selected as required. All buffers or lists must be located on segment addresses (32 bytes segmentation).

| 1FFFh |          | Code Area fo            | or the Internal C31                          |

|-------|----------|-------------------------|----------------------------------------------|

|       |          | Communic-<br>ation Area | Buffer Area                                  |

| 08A0h |          |                         |                                              |

| 0840h |          |                         | Organizational<br>Parameters                 |

| 0800h | RAM      |                         | Internal Work Area                           |

|       |          |                         | SSC-Interface                                |

| 0000h | Register |                         | Control Unit Parameters<br>Latches/Registers |

Table 3.1-1: Memory Area Distribution in the Internal RAM of the DPC31

The stack for the sequential control system needs 64 bytes. A buffer for temporarily storing the receive message requires 32 bytes.

# 3.2 Control Unit Parameters (Latches/Registers)

The register cells that are, for example, in the interrupt controller and the DPS control units, are located in the address area of 0000-003Ch (XDATA). These cells can either be read or written only. The address assignments are shown in Table 3.2-1. When writing the register cells, the unassigned bit positions are 'don't care'.

| Address | Name                                 | Meaning (read access!)                                        |

|---------|--------------------------------------|---------------------------------------------------------------|

| 0000h   | Int-Req-Reg <sub>70</sub>            | Interrupt Controller Register                                 |

| 0001h   | Int-Req-Reg <sub>158</sub>           |                                                               |

| 0002h   | Int-Req-Reg <sub>2316</sub>          |                                                               |

| 0003h   | Int-Req-Reg <sub>2824</sub>          |                                                               |

| 0004h   | Int-Reg <sub>70</sub>                |                                                               |

| 0005h   | Int-Reg <sub>158</sub>               |                                                               |

| 0006h   | Int-Reg <sub>2316</sub>              |                                                               |

| 0007h   | Int-Reg <sub>2824</sub>              |                                                               |

| 0008h   | -                                    |                                                               |

|         | Reserved                             |                                                               |

| 000Fh   |                                      |                                                               |

| 0010h   | C31_Control Register <sub>70</sub>   | Refer to Chapter 4                                            |

| 0011h   | -                                    |                                                               |

|         | Reserved                             |                                                               |

| 001Fh   |                                      |                                                               |

| 0020h   | SSC_Rcv-Buf <sub>70</sub>            | Receive buffer of the SSC interface                           |

| 0021h   | SSC_Sts-Reg <sub>30</sub>            | Status register of the SSC interface                          |

| 0022h   | SSC_Ctrl1-Reg <sub>70</sub>          | Control register of the SSC interface                         |

| 0023h   | SSC_Ctrl2-Reg <sub>20</sub>          | Control register of the SSC interface                         |

| 0024h   |                                      |                                                               |

|         | Reserved                             |                                                               |

| 002Fh   |                                      |                                                               |

| 0030h   | User_SSA_Ok Cmd <sub>10</sub>        | The user acknowledges the user SSA data of an SSA message     |

|         |                                      | positively                                                    |

| 0031h   | User_Prm_Ok Cmd <sub>10</sub>        | The user acknowledges the user parameter assignment data of a |

|         |                                      | prm message positively                                        |

| 0032h   | User_Prm_Not_Ok Cmd <sub>10</sub>    | The user acknowledges the user parameter assignment data of a |

|         |                                      | prm message negatively                                        |

| 0033h   | Reserved                             |                                                               |

| 0034h   |                                      |                                                               |

| 0035h   | User_Cfg_Ok Cmd <sub>10</sub>        | The user acknowledges the configuring data of a CfG message   |

|         |                                      | positively                                                    |

| 0036h   | User_Cfg_Not_Ok-Cmd <sub>10</sub>    | The user acknowledges the configuring data of a Cfg message   |

|         |                                      | negatively                                                    |

| 0037h   | User_Diag_Read-Cmd                   | The user makes a new diag buffer available                    |

| 0038h   | User_Get_Cfg_Read-Cmd                | The user makes a new Get_Cfg buffer available                 |

| 0039h   | User_New_Din-Cmd <sub>10</sub>       | The user makes a new Din buffer available                     |

| 003Ah   | User_Din_Puffer-State <sub>70</sub>  | The user reads the current Din buffer assignment              |

| 003Bh   | User_New_Dout-Cmd <sub>30</sub>      | The user fetches the last Dout buffer from the N state        |

| 003Ch   | User_Dout_Puffer-State <sub>70</sub> | The user reads the current Dout buffer assignment             |

| 003Dh   | _                                    |                                                               |

|         | Reserved                             |                                                               |

| 07FFh   |                                      |                                                               |

Table 3.2-1: Assignment of the Internal Register Cells for READ

| 0000h | Int-Req-Reg <sub>70</sub>          | Interrupt Controller Register                            |

|-------|------------------------------------|----------------------------------------------------------|

| 0001h | Int-Req-Reg <sub>158</sub>         |                                                          |

| 0002h | Int-Req-Reg <sub>2316</sub>        |                                                          |

| 0003h | Int-Req-Reg <sub>2824</sub>        |                                                          |

| 0004h | Int-Ack-Reg <sub>70</sub>          |                                                          |

| 0005h | Int-Ack-Reg <sub>158</sub>         |                                                          |

| 0006h | Int-Ack-Reg <sub>2316</sub>        |                                                          |

| 0007h | Int-Ack-Reg <sub>2824</sub>        |                                                          |

| 0008h | Int-Mask-Reg <sub>70</sub>         |                                                          |

| 0009h | Int-Mask-Reg <sub>158</sub>        |                                                          |

| 000Ah | Int-Mask-Reg <sub>2316</sub>       |                                                          |

| 000Bh | Int-Mask-Reg <sub>2824</sub>       |                                                          |

| 000Ch | Int-EOI-Reg <sub>0</sub>           |                                                          |

| 000Dh |                                    |                                                          |

| 000Eh | reserved                           |                                                          |

| 000Fh |                                    |                                                          |