# **User Description**

Integrated Circuit for Electrically Conditioning the Optical Signal When Transmitting Data by Means of Fiber-Optic Cables

(M4A3-64/32-12VI)

Version: 0.3 Date: July 18, 2000

### **Liability Exclusion**

Although we have tested the contents of this document regarding agreement with the described hardware and software, deviations cannot be ruled out, and complete agreement cannot be guaranteed. However, the data in this document is checked periodically. Necessary corrections are included in subsequent versions. We gratefully accept suggestions for improvement.

#### Copyright

Copyright © Siemens AG 2000. Unless permission has been expressly granted, passing on this document or copying it, or using and sharing its content is not allowed. Offenders will be held liable. All rights reserved, in the event a patent is granted, or a utility model or design is registered.

The brand names SIMATIC, SINEC L2 are protected legally for Siemens AG through application/registration. All other product and system names are (registered) brand names of their respective proprietor, and are to be treated as such

Subject to technical changes

Page 2 Version: 0. 3 User Description

| 1.       | GENERAL                                                                                  | 1 |

|----------|------------------------------------------------------------------------------------------|---|

| 2.       | BLOCK DIAGRAM                                                                            | 1 |

| 3.<br>CO | APPLICATION EXAMPLE: CHIP FOR CONDITIONING THE OPTICAL SIGNAL IN NECTION WITH A DP_ASIC7 | 7 |

| 4.       | PARTS LIST                                                                               | ) |

| 5.       | LITERATURE ON THE INTERNET                                                               | ) |

| 6.       | FIBER-OPTIC COMPONENTS                                                                   | ) |

| 7.       | CONFIGURATION10                                                                          | ) |

| 8.       | UP INTERFACE                                                                             | ) |

| 9.       | ISP/IN-CIRCUIT TEST/CHIP HANDLING10                                                      | ) |

| 10.      | APPLICATION NOTES11                                                                      | I |

| 11.      | TECHNICAL SPECIFICATIONS12                                                               | 2 |

| 12.      | TIME RESPONSE FOR CASCADING13                                                            | 3 |

| 13.      | CASCADING DEPTH AND STANDARD DP PROFILE13                                                | 3 |

| 14.      | PIN ASSIGNMENT FOR THE CHIP FOR CONDITIONING THE OPTICAL SIGNAL14                        | 1 |

### 1. General

The integrated circuit for conditioning the optical signal is an interface circuit for **connecting a station** on the fiber-optic (FO) bus, for **retiming** (= compensating for signal distortions) and **repeating** (= message frame routing) DP message frames on PROFIBUS DP/FO.

Areas of Application:

- Slaves in an optical ring

- Slaves in an open line structure

- · Masters in an open line structure

In addition to the integrated circuit for conditioning the optical signal, fiber-optic components (transmitter/receiver) and external send drivers are needed.

Message frames are not evaluated in the circuit for conditioning the optical signal. The chip provides a TTL interface to connect a DP ASIC for the actual evaluation/processing of the message frames.

An RS 485 transceiver can (with restrictions) be connected to the TTL interface. Copper segments are not to be connected here! The cable distortions on the RS 485 interface must not exceed +/- 20 ns. This application is intended for connecting a module with a copper interface to the fiber-optic bus. Here, only a short point-to-point connection terminated on both ends is to be used.

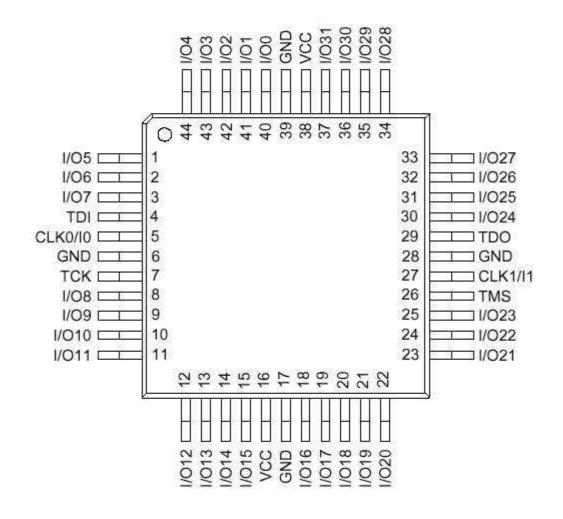

The integrated circuit is implemented with a 44-pin chip in TQPF casing and reduced power loss. The complete and operational chip can be ordered from Siemens AG (Automation & Drives) under the numbers 6ES7 **195-0EA00-0XA0** - 10 Pieces and **6ES7 195-0EA10-0XA0** - 160 Pieces.

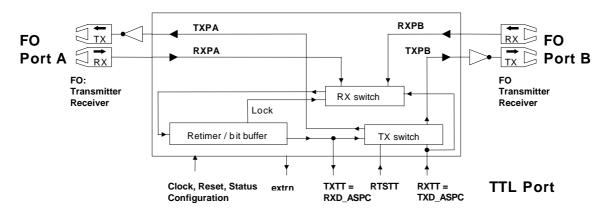

### 2. Block Diagram

| Signal Ports/Chip Segments       | Function                                                                                                                                                                                                                           |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FO Port A                        | Line: fiber-optic connection duplex line "A" (Port A/B = symmetrical)                                                                                                                                                              |

| FO Port B                        | <b>Line:</b> fiber-optic connection duplex line "B" (Port A/B = symmetrical)                                                                                                                                                       |

| TTL Port (RXD, TXD, RTS)         | TTL side; direct connection to a PROFIBUS ASIC (TTL) Connection to an RS 485 driver (reti == high)                                                                                                                                 |

| extrn                            | Driver_Enable for external RS 485 transceiver                                                                                                                                                                                      |

| Clock/Reset/Status/Configuration | Auxiliary signals                                                                                                                                                                                                                  |

| RX switch (lock)                 | Prioritizes the receive signals and selects a preferred direction. The switch switches the RX signal to the retimer/bit buffer for further processing.                                                                             |

| Retimer/Bit buffer               | The input signal is scanned and distortions are corrected. A bit buffer FIFO compensates for clock drifts from the external transmitter and the chip for conditioning the signal. The corrected signal is routed to the TX switch. |

| TX switch                        | Depending on the prioritized preferred direction, the signal flow is routed to the FOSCI (fiber-optic cable coupler) ports.                                                                                                        |

Page 4 Version: 0. 3 User Description

This chip is a three-gate chip that connects three bidirectional ports with each other. These are the FO ports A and B, and the TTL port.

During an idle phase (message frame interval), the RX switch monitors the Receive lines of all three ports. If an RX\_Port becomes active, it is prioritized. The Receive mode of the remaining ports is switched off.

The received signal is conditioned in the retimer/bit buffer, and buffered.

The transmission switch accepts the data from the bit buffer and routes it to the transmission outputs according to the following transfer scheme.

| Rece       | ived from Interfa | ice    | Ro        | uting to Interface | e        |

|------------|-------------------|--------|-----------|--------------------|----------|

| RX_ Port_A | high              | high   | high      | TX_Port_B          | TX_TTL   |

| high       | RX_Port_B         | high   | TX_Port_A | high               | TX_TTL   |

| high       | high              | RX TTL | TX Port A | TX Port B          | ECHO 1:1 |

There is a time delay between the received signal and the transmitted signal due to the scanning process and the buffer.

At TXTT, the signals received at the TTL port (RXTT) are mirrored to the source. Some DP ASICs expect this echo function. The echo function is NOT time-delayed (that is, except for gate runtimes identical with RXTT).

An RS 485 transceiver can be connected to the TTL port.

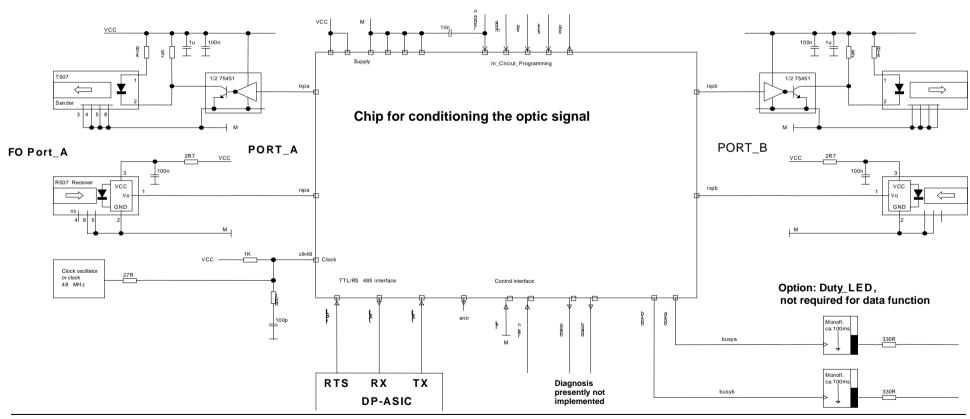

# 3. Application Example:

# Chip for Conditioning the Optical Signal in Connection with a DP\_ASIC

Page 7 Version: 0. 3 User Description

### 4. Parts List

| Chip for conditioning the optical signal | 6ES7 195-0EA00-0XA0<br>6ES7 195-0EA10-0XA0 | Siemens            |

|------------------------------------------|--------------------------------------------|--------------------|

| Transmitter                              | QFBR T507                                  | Hewlett<br>Packard |

| Receiver                                 | QFBR R507                                  | Hewlett<br>Packard |

#### Note:

Fiber-optic receivers/transmitters are components of the HP series 508.

| Function    | Standard Device 10 Mbits | Selected Device 12 Mbits |  |

|-------------|--------------------------|--------------------------|--|

| Transmitter | HFBR-1528                | QFBR-T507                |  |

| Receiver    | HFBR-2528                | QFBR-R507                |  |

### Note:

The pair receiver/sender must be latched prior to soldering.

### 5. Literature on the Internet

### **Hewlett-Packard**

http://www.hp.com http://www.agilent.com Homepage HP Components Internet address of Agilent Technologies:

### 6. Fiber-Optic Components

### **POF Fiber-Optic Cable**

see: Catalog Siemens IK 10, pages 10,11 CUPOFLEX Simplex Core, unassembled CUPOFLEX Duplex Core, unassembled

5DX6 312-4AA01 5DX6 322-4AA01

# 7. Configuration

| Port      | Function/Application                                                                       |

|-----------|--------------------------------------------------------------------------------------------|

| RETI      | This control port is wired statically. It specifies whether the signal RXTT is switched by |

|           | means of the "detour" retimer, or directly to the TX switch.                               |

| RETI = lo | If the ASPC2/SPC3 ASIC is coupled directly (TTL signals) with the chip for conditioning    |

|           | the optical signal, the send signal TX_ASIC == RXTT is not significantly distorted, and    |

|           | does not have to be "retimed" for that reason.                                             |

|           | Note: RTS must be wired. If RETI=lo, the RX switch has no lead time for prioritizing the   |

|           | receive port. This must be done with RTS which the ASIC activates shortly before it        |

|           | transmits.                                                                                 |

| RETI = hi | The signal received at RXTT is processed by means of the retimer.                          |

|           | This is a must if an RS 485 transceiver is connected at the chip for conditioning the      |

|           | optical signal.                                                                            |

|           | This also applies if the RTS is applied to the RS 485 interface.                           |

| RTSTT     | High active input. Send request by the ASIC to the chip for conditioning the optical       |

|           | signal. Is evaluated by the receive port prioritization (>> a floating input blocks the    |

|           | FOSCI (fiber-optic cable coupler) because it is interpreted as a continuous request).      |

# 8. μP Interface

These signals remain "reserved".

# 9. ISP/In-Circuit Test/Chip Handling

By means of the pin "ispen $_n$ ", the chip is switched to Tristate . All pins are inputs with integrated pull-up resistors.

TQPF casings must be dried prior to soldering.

### 10. Application Notes

**ISP:** The manufacturer recommends decoupling the input ispen\_n by means of 10 nF capacitor to GND to prevent interference during operation.

**QFBR R507:** Filtering the VCC of the fiber-optic receiver as described in the HP data sheet must be adhered to. The backup capacitor must be located in the immediate vicinity of the receiver. (Error: the receiver may start oscillating through its input noise, even without light incidence. Viewed on an oscilloscope, this interference can only be distinguished with difficulty from a 12-Mbps message frame. The interference blocks the chip for conditioning the optical signal and creates "data scrap" in the entire fiber-optic network.)

**QFBR R507:** The casing material of the receiver is electrically conductive. The wire link must be placed on GND or shield.

**QFBR R507**, **mechanical destruction**: In one case, the receiver was destroyed through a POF fiber-optic cable. The error was a sporadic receive interruption, depending on the mechanical load on the chip. Cause: In a fiber-optic connector that was pressed together poorly, the light conducting core was movable in the connector and protruded under pressure up to 1.5 mm.

**Clock 48 MHz:** The clock does not have to be in-phase or identical with the operating clock of the ASIC. The chip for conditioning the optical signal synchronizes all input signals.

**Clock 48 MHz:** The timing circuit is to be terminated at the chip, in order to avoid overswings and underswings. The dimensioning in the application circuit can serve as a guide. The quality of the scan requires a pulse duty factor that is as close as possible to 50:50. The pulse symmetry of the oscillator should not be impaired because of the termination.

**busya**, **busyb**: By means of a retriggerable monoflop circuit, an LED can be connected optionally to these ports that displays the signal flow.

diaga, diagb: Unused reserve pins. Are reserved for use in the diagnostic concept.

### **Commissioning Tips:**

- Isolate the chip for conditioning the optical signal from the fiber-optic network, to exclude outside influences.

- Stimulate the chip for conditioning the optical signal alternately at all three ports at the input.

- Rectangular signal 1 MHz to 6 MHz is suitable (preferably 3 / 1.5 / 0.75 MHz).

- At the respective "opposing" outputs, there must be a reaction to this signal.

- If this does not happen, the chip for conditioning the optical signal could be locked into a fixed data direction through RTSTT or interference on another input.

- Internal masking of a fiber-optic port is recognizable from the idle level of the associated Busy\_Signal.

- RXPA >> busya, RXPB >> busyb.

Frequent error sources during the test phase were:

- Wrong or interchanged (RX/TX) fiber-optic components

- System blockage because of self-interference of a receiver

- Floating RTSTT (as a rule through line interruption)

### 11. Technical Specifications

Transmission current LED 60 mA / each LED

Permitted FO\_length POF 50 m Permitted FO\_length HCS 300 m

Optical power reserve 3 dB (for maximum lengths/expanded temperature range)

Expanded temperature range, QFBR HP components are specified correspondingly

Moisture condensation HP\_FO No electrical destruction; same-design 5MBit types are

qualified. Damping in the case of condensation was measured.

It is not a detriment.

Current consumption 1032E-125 < 220 mA Caution: cooling problem, Tcase = 85 °C

Permitted range T\_Junction is not exceeded.

Cascading depth 32 stations starting with the master (included)

(2 \* 32, if master is positioned topologically in the center)

Current supply + 3.0 V to + 3.6 VOperating temperature  $-40 \,^{\circ}\text{C}$  to  $+85 \,^{\circ}\text{C}$

Ambient temperature - 40 °C to + 85 °C

### 3.3-V Type:

44-pin TQFP case

Information regarding 3/5-V mixed design: 3.3-V chip has TTL\_input thresholds and 3-V output swing. All I/O on the 3-V type tolerate 5-V input levels.

All I/O have integrated pull-up resistors.

### 12. Time Response for Cascading

Functional Background:

- Each chip for conditioning the optical signal has a bit buffer (FIFO) to buffer quartz tolerances by means of a message frame.

- The FIFO size used is selected so that +/- 100 ppm frequency differences can be intercepted by means of a message frame of maximum length.

- First, the FIFO is filled up to 50% prior to further transmission. This provides for a reserve against underflow.

- Depending on the guartz ratio of source and sink, there is a tendency toward overflow or underflow.

- Regarding a two-way route over the segment, overflow and underflow of two partners are corrected into an average.

- Because of the retimer procedure, the digital delay caused by the chip for conditioning the optical signal

does not depend on the baud rate.

| Component                                                   | Delay        | Explanation                                                                                                                                                                          |

|-------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Light runtime in the fiber-optic cable                      | 5 ns/m       | Is not subject to fluctuations                                                                                                                                                       |

| Analog delay through the fiber-<br>optic components RX + TX | 130ns 150ns  | Time depends on the level. Temperature behavior not clarified.                                                                                                                       |

| Minimum digital delay                                       | 3.5 x 83.3ns | Pulse of the chip for conditioning the optical signal is faster than the source.                                                                                                     |

| Maximum digital delay                                       | 8.5 x 83.3ns | Pulse of the chip for conditioning the optical signal is slower than the source.                                                                                                     |

| Median digital delay                                        | 6.0 x 83.3ns | This value is applied to the response time on the line, request <>response. In the case of a two-way route by way of the same segment, the median value is <b>always</b> the result. |

### 13. Cascading Depth and Standard DP Profile

In contrast to a copper segment where the stations only "tap" the signal, in the fiber-optic segment each station is a repeater. This results in increased demands on the time response of the segment. In the case of the Std\_DP profile in the configuration tool, the time reserved for the propagation delay in the system is the difference of the slot time minus tsdr\_max.

The table below provides a guide regarding the cascading depth of the chip for conditioning the optical signal if there is one 50-m fiber-optic segment each between two stations and the standard DP profile timing must be adhered to in the worst case.

| Baud Rate | Cascading         |

|-----------|-------------------|

| 12 Mbaud  | 9 / 32 (*)        |

| 6 Mbaud   | Baud rate blocked |

| 3 Mbaud   | Baud rate blocked |

| 1.5 Mbaud | 32                |

| Rest      | 32                |

<sup>(\*) 32</sup> stations if the DP profile is adapted to the propagation delay.

#### As maximum cascading depth including the master, 32 is specified.

If the runtime calculation results in a cascading depth larger than 32, the valid maximum therefore is 32.

#### Note:

If the (mono) master of a fiber-optic system is topologically in the center, the maximum cascading depth is permitted for each fiber-optic subsegment that is connected to the master.

# 14. Pin Assignment for the Chip for Conditioning the Optical Signal

| Pin No. | Type                | Attribute                                                                                            | Function : Signal Pin                                                                                                                                                                                                 |

|---------|---------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5       | in                  | clock,                                                                                               | Main clock. The clock symmetry is very important to the                                                                                                                                                               |

|         |                     | pull-up                                                                                              | function of the circuit. +/-5% dissymmetry should be the                                                                                                                                                              |

|         |                     |                                                                                                      | objective.                                                                                                                                                                                                            |

| 31      | 29                  |                                                                                                      | Power_On_Reset. Caution! Don't connect this pin with the                                                                                                                                                              |

|         |                     | up                                                                                                   | software reset port of the ASPC2 / SPCx / DPC31 ASIC. The                                                                                                                                                             |

|         |                     |                                                                                                      | FOSCI (fiber-optic cable coupler) is disabled under reset. A SW driver that resets "its" ASIC because of a crash must not                                                                                             |

|         |                     |                                                                                                      | interrupt the line.                                                                                                                                                                                                   |

| 42      | in                  | pull-up                                                                                              | Receive Data Port A                                                                                                                                                                                                   |

| 24      | in                  | pull-up                                                                                              | Receive Data Port B                                                                                                                                                                                                   |

| 22      | in                  | pull-up                                                                                              | Receive Data Port TTL. CAUTION! Risk of confusion: Port rxtt                                                                                                                                                          |

|         |                     |                                                                                                      | is wired to the signal <b>tx</b> d of the ASIC.                                                                                                                                                                       |

|         |                     |                                                                                                      |                                                                                                                                                                                                                       |

| 2       | in                  | pull-up                                                                                              | RTS, send request by the DP ASIC.                                                                                                                                                                                     |

|         |                     |                                                                                                      | If not used, low-resistance pulldown resistor required (1 K).                                                                                                                                                         |

|         |                     | •                                                                                                    |                                                                                                                                                                                                                       |

|         |                     |                                                                                                      | Transmit data to Port A                                                                                                                                                                                               |

|         |                     |                                                                                                      | Transmit data to Port B                                                                                                                                                                                               |

| 13      | out                 | active                                                                                               | Transmit data to Port TTL. CAUTION! Risk of confusion: Port                                                                                                                                                           |

|         |                     |                                                                                                      | txtt is wired to the signal rxd of the ASIC.                                                                                                                                                                          |

| 25      | out                 | active                                                                                               | Trigger signal for a Startup_LED Channel A; refer to standard                                                                                                                                                         |

|         |                     |                                                                                                      | application. Function is not used.                                                                                                                                                                                    |

|         | out                 | active                                                                                               | Same as busya                                                                                                                                                                                                         |

| ·       |                     |                                                                                                      | Positive supply voltage 5 V                                                                                                                                                                                           |

|         |                     |                                                                                                      | "Ground" supply of chip                                                                                                                                                                                               |

|         |                     |                                                                                                      |                                                                                                                                                                                                                       |

|         | in                  | pull-up                                                                                              | The connections remain open on the module.                                                                                                                                                                            |

| der     |                     |                                                                                                      |                                                                                                                                                                                                                       |

|         |                     |                                                                                                      |                                                                                                                                                                                                                       |

|         | 5<br>31<br>42<br>24 | 5 in  31 29  42 in 24 in 22 in  2 in  34 in 15 out 19 out 13 out 25 out  16,38 6,17, 28,39 Remain in | 5 in clock, pull-up  31 29 In, pull-up  42 in pull-up  24 in pull-up  22 in pull-up  34 in pull-down  15 out active  19 out active  13 out active  25 out active  35 out active  16,38 6,17, 28,39  Remain in pull-up |